# Untersuchung von ESD-Einkopplungen auf Platinenebene

Friedrich zur Nieden, TU-Dortmund, AG Bordsysteme, Dortmund, Germany Stanislav Scheier, TU-Dortmund, AG Bordsysteme, Dortmund, Germany Bastian Arndt, AVL-Trimerics GmbH, Regensburg, Germany Stephan Frei, TU-Dortmund, AG Bordsysteme, Dortmund, Germany

### 1 Einleitung

Die Strukturgrößen in den ICs werden durch die Anwendung neuer Technologien kleiner. Für den ESD-Schutz stellt die Miniaturisierung eine Herausforderung dar. Im ESD-Fall müssen kleinere Halbleiterstrukturen den ESD-Strom tragen. Die durch Normen und andere Vereinbarungen vorgegebenen Spezifikation für den ESDbisher Konsortium vieler Schutz blieben unverändert. Ein wichtiger Halbleiterhersteller schlug vor einigen Jahren die Herabsetzung der bisher üblichen HBM Prüfschärfe für IC Pins von 2 kV auf 1 kV vor [1]. Statistische Untersuchungen des Konsortiums weisen darauf hin, dass diese Maßnahme sich nicht negativ auf Ausfallraten von Systemen auswirken wird.

Die vom Konsortium vorgeschlagenen Maßnahmen sollen jedoch nicht für alle IC-Pins gelten. Es kann zwischen globalen und lokalen Pins unterschieden werden. Globale IC-Eingänge sind im Gegensatz zu lokalen Pins direkt mit dem Gerätestecker des elektronischen Systems verbunden und können deshalb elektrostatischen Entladungen mit größeren Amplituden und Energien ausgesetzt sein.

In der Automobilindustrie werden die Auswirkungen der Reduzierung der HBM-Festigkeit auf IC-Ebene kontrovers diskutiert [2]. Da die globalen Pins in den Systemprüfungen besonders im Kfz-Bereich weiterhin hoch belastet werden, kann durch Verkopplungen auf Platinen ein nur noch schwach geschützter lokaler Pin aufgrund der niedrigen Eigenfestigkeit gefährdet sein. Weiterhin sind die Auswirkungen auf bestehende Schutzkonzepte, die auf diskrete ESD-Schutzelemente zurückgreifen, unklar.

Die Ausfallspannung eines ICs kann durch die Verwendung von Schutzelementen nur in Grenzen angehoben werden [3]. Somit könnte die Reduzierung der ESD-Festigkeit auf IC-Ebene dazu führen, dass vorhandene und erprobte Schutzkonzepte für empfindliche Systeme nicht mehr ausreichen werden. In diesem Beitrag werden mögliche Konsequenzen durch Überkopplungen untersucht. Eine Demonstrator-Platine wurde unter Berücksichtigung typischer Konfigurationen, die in der Automobilindustrie vorkommen, entwickelt. Die Koppeleigenschaften zwischen Leitungen werden untersucht. Typische Kfz-ICs, werden dabei als realistische Abschlüsse für die Leitungen verwendet. Das Ausfallverhalten der ICs kann durch Messungen und Simulationen untersucht werden [5] [6]. Für die IC-Abschlüsse wurden thermische ESD-Ausfallmodelle erstellt. Durch Veränderung der thermischen Eigenschaften kann die ESD-Festigkeit im Modell beliebig angepasst werden. Durch der Leitungsparameter und der Abschlüsse können kritische Konfigurationen bestimmt werden.

#### 2 Demonstrator-Platine

Für die Untersuchungen wurde eine 160 mm x 100 mm große Demonstrator-Platine verwendet. Diese ist zweilagig aufgebaut, wobei eine Lage als Massefläche ausgeführt ist. Das FR4-Material des Dielektrikums hat eine Dicke von 1,55 mm. Die Dicke der Kupferleiterbahnen beträgt 35  $\mu$ m. Zur Untersuchung von Koppeleffekten wurden zwei 110 mm lange und 1 mm breite Leiterbahnen in einem Abstand von 0,5 mm verwendet. Über Lötpads an den Enden können die Bahnen mit verschiedenen Abschlüssen und ESD-Schutzelementen versehen werden. Für Messungen kann ein ESD-Generator über einen 32-poligen Stecker entladen werden und Strom- und Spannungssignale über aufgelötete SMA-Buchsen mit dem Oszilloskop gemessen werden. Auf der Platine sind Sockel für CAN- und LINtransceiver sowie für einen  $\mu$ C verbaut, um die IC-ESD-Festigkeit verschiedener Pins zu überprüfen.

### 3 Modellierung

In diesem Kapitel werden Modelle vorgestellt, die für die simulationsbasierten Untersuchungen notwendig waren. Leitungsmodelle, IC-Modelle und die Modelle der ESD-Pulsquellen wurden zu einem Gesamtsystem für die Simulation miteinander verbunden. Alle Untersuchungen wurden in VHDL-AMS durchgeführt.

#### 1.1 Pulsquellen

Für die Untersuchungen wurden Netzwerkmodelle verschiedener Pulsquellen eingesetzt. Messungen und Simulationen auf Systemebene wurden mit einem Noiseken TC-815R IEC-ESD-Generator durchgeführt. Ein äquivalentes Modell aus konzentrierten Elementen wurde in [7] vorgestellt. Für die Charakterisierung von ICs wird ein Transmission-Line-Pulser (TLP) eingesetzt. Der Puls wird durch eine vorgeladene 50  $\Omega$  Leitung und weitere Elemente zur Abbildung der Anstiegszeiten und des Reflektionsverhaltens modelliert [7] [8]. Für die Untersuchungen der Auswirkungen der Herabsetzung der ESD-Festigkeit auf IC-Ebene wurde ein Modell eines HBM-Generators aus konzentrierten Elementen [3] eingesetzt.

#### 1.2 Modellierung von Leitungsstrukturen auf Platinen

Für die Simulation der Übertragungseigenschaften von und der Kopplung zwischen Leitungsstrukturen können Mehrleitermodelle verwendet werden. Geeignete Modelle werden in [9] beschrieben. Die Modellparameter können mit Kenntnis der Materialien und der Abmessungen berechnet werden [10] [11].

### 1.3 Modellierung von Halbleiterstrukturen

Das statische Strom- Spannungsverhalten von Halbleiterbauelementen wird durch Messungen mit einem Kennlinienschreiber und für höhere Ströme mit einem TLP [13] bestimmt. Die statische Kennlinie wird zusammen mit einem elektrischen Netzwerk zur Abbildung der frequenzabhängigen Eigenschaften, die mit dem Netzwerkanalysator (NWA) gemessen werden, im Modell hinterlegt. Die Modellierung von ESD-Schutzelementen und IC-Eingängen wurde in [4] [5] [6] [8] beschrieben.

Die ESD-Zerstörfestigkeit der für diese Untersuchungen verwendeten ICs wird durch das Erreichen einer kritischen Schmelztemperatur des Siliziums modelliert [6]. Die Zerstörenergie wurde durch Messungen mit dem TLP unter Variation der Pulsbreite ermittelt und in dem Modell abgebildet.

| IC (Pin)                 | Ausfallenergie [μJ]                                 |             |            |  |  |

|--------------------------|-----------------------------------------------------|-------------|------------|--|--|

|                          | Messung 2 kV HBM (Faktor-Mess) 1 kV HBM (Faktor-2kV |             |            |  |  |

| Infineon µC-XC864 (DATA) | 12,3                                                | 0,82 (15,0) | 0,35 (2,4) |  |  |

| Atmel LIN-ATA662C (TXD)  | 7,4                                                 | 1,7 (4,4)   | 0,7 (2,4)  |  |  |

| NXP CAN-TJA1041T (CANH)  | 19,2                                                | 5,2 (3,7)   | 2,1 (2,5)  |  |  |

Tabelle 1: Ermittelte Ausfallenergien der Original- und der skalierten Modelle von 3 IC-Pins

Um die Auswirkung der geplanten Herabsetzung der HBM-Festigkeit von ICs zu untersuchen, wurde die ESD-Festigkeit der zuvor durch Messungen verifizierten Modelle herabgesetzt, sodass die Energie zum Erreichen der Zerstörtemperatur bei einem 1 kV oder 2 kV HBM-Puls simuliert wird. Bei der Methode zur Skalierung der ESD-Festigkeit werden die thermische Kapazität und der thermische Widerstand der IC-Modelle an die neue Ausfallenergie angepasst [6]. Die durch Messungen und der Skalierung ermittelten Ausfallenergien IC-Modelle können aus Tabelle 1 entnommen werden. Die kleinste Ausfallenergie beträgt demnach 350 nJ für das 1 kV HBM-Modell des  $\mu$ C-DATA-Pins.

### 4 Messung

Zur Überprüfung der Anwendbarkeit der Modelle für abschließende Untersuchungen werden Messdaten mit Simulationsdaten verglichen. Die Demonstrator-Platine wurde verwendet, um Messungen an geeigneten Konfigurationen durchzuführen. Wichtige Ergebnisse werden nachfolgend dargestellt. Detaillierte Untersuchungsergebnisse können aus [14] entnommen werden.

1.4 Leitungseinkopplung / Messtechnische Analyse und Verifikation der Simulationsmethodik

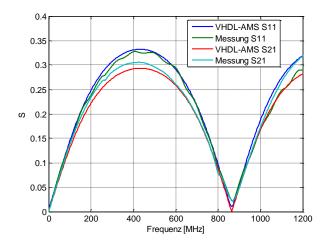

Für den Vergleich von Messung und Simulation der Koppeleigenschaften von Leiterbahnen werden die entsprechenden Leitungen der Länge 110 mm auf dem Demonstrator verwendet. Die Leitungen haben einen Abstand von 0,5 mm und sind an einem Ende mit 51  $\Omega$  Widerständen abgeschlossen. Ein NWA wird über zwei SMA-Buchsen mit jeweils einem Ende der Leitungen verbunden. Die Parameter des Leitungsmodells wurden zu  $Z_{\text{Gegentakt}}=105,2~\Omega$  und  $Z_{\text{Gleichtakt}}=52,5~\Omega$  berechnet. Die verschiedenen Ausbreitungsgeschwindigkeiten der modalen Gleich- und Gegentaktgrößen haben einen zu vernachlässigenden Einfluss und wurden zu v=172.9·10 $^6$  m/s gesetzt. Die gemessenen und simulierten Reflexions- und Transmissionsparameter sind in Abbildung 1 dargestellt. Die Kurven stimmen für beide Parameter gut überein.

Abbildung 1: Vergleich von Messung und Simulation der Leitungsverkopplung im Frequenzbereich

#### 1.5 Verifikation der IC-Modelle

Die Modellierung der ESD-Festigkeit von ICs basiert auf den Ergebnissen aus der Charakterisierung mit dem TLP. Für die Verifizierung der IC-Modelle wurde die ESD-Festigkeit unter Berücksichtigung der Konfiguration auf der Demonstrator-Platine simuliert und anschließend mit einem IEC-ESD-Generator durch Messung ermittelt. Nachfolgend werden Ergebnisse für den  $\mu$ C-DATA-Pin exemplarisch dargestellt. Ergebnisse für weitere IC-Eingänge werden in [6] [14] dargestellt.

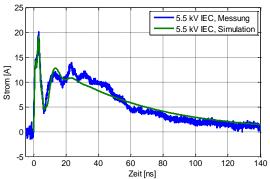

Abbildung 2: Vergleich von Messung und Simulation für eine IEC-Entladung mit  $\mu C$

| ESD-<br>Pulsquelle | U <sub>Lade</sub><br>[V] | V <sub>IC ,max</sub><br>[V] | I <sub>IC, max</sub><br>[A] | E <sub>Ausfall</sub><br>[µJ] |

|--------------------|--------------------------|-----------------------------|-----------------------------|------------------------------|

| IEC<br>NoiseKen    | 5500                     | 53.4                        | 27.1                        | 11.3                         |

| TLP 100 ns         | 450                      | 95.4                        | 9.0                         | 12.3                         |

Tabelle 2: Gemessene Größen für TLP und ESD-Generator, die zum Ausfall des μC führten

Der Entladestrom, welcher zur Zerstörung des µC führte, wird in Abbildung 2 gezeigt. Messung und Simulation stimmen gut überein. In Tabelle 2 werden die gemessenen Größen, die zur Zerstörung des µC führen, für eine TLP-Entladung mit 100 ns Pulsbreite und eine IEC-Generator-Entladung gegenübergestellt. Die ermittelten Ausfallenergien weichen nur geringfügig voneinander ab. Diese und weitere hier nicht dargestellte Messreihen bestätigen die Annahme, dass viele Ausfälle durch thermische Zerstörung verursacht werden und das thermische Ausfallmodell korrekt ist. Die nominelle HBM-Festigkeit des Pins beträgt laut Datenblatt 2 kV.

### 5 Simulationsbasierte Analysen

Die Leitungstopologie und die Abschlusskonfiguration werden in der Simulation systematisch verändert. In Abschnitt 1.6 werden bei Variation von

Konfigurationsparametern übergekoppelte Signale simuliert. In Kapitel 1.7 wird eine Topologie simuliert, welche als typisch für Kfz-Elektronik gesehen werden kann. In Abschnitt 1.8 und 1.9 werden schließlich kritische Konfigurationen herausgestellt.

# 1.6 Einfluss der Leitungslänge und des Abstands auf die Überkopplung

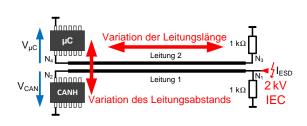

Um die Auswirkung der Leitungsverkopplung auf lokale IC-Pins bei ESD zu untersuchen, wurde eine Konfiguration mit zwei parallelen Leitungen simuliert. Das Schaltbild ist in Abbildung 3 dargestellt. Leitung 1 ist an einem Ende mit einem globalen IC-Pin abgeschlossen, während Leitung 2 mit einem  $\mu$ C-Pin mit geringerer ESD-Festigkeit verbunden ist. Die Energie am  $\mu$ C-DATA-Pin wird für eine 2 kV IEC-Entladung auf Leitung 1 simuliert.

Abbildung 3: Aufbau zur Untersuchung der Leitungstopologie auf die ESD-Einkopplung

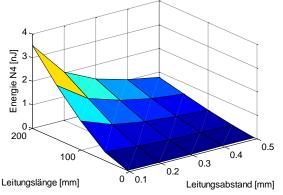

Abbildung 4: Energie an Knoten N<sub>4</sub> bei Variation der Leitungslänge und des Leitungsabstands

In Abbildung 4 wird der Einfluss der Parameter Leitungslänge und Leitungsabstand auf die am µC simulierte Energie dargestellt. Die eingekoppelte Energie erhöht sich mit größeren Leitungslängen und kleinerem Leiterbahnabstand.

### 1.7 Simulation realitätsnaher Leitungstopologien

Die bisher gezeigten Untersuchungen können zum Teil nicht als typisch angesehen werden. Extreme Bedingungen wurden bewusst für die Analysen hergestellt. Für die weitere Untersuchung werden realitätsnahe Konfigurationen verwendet. Die Parameter für das VHDL-AMS-Leitungsmodell werden in der Simulation angepasst.

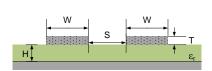

Abbildung 5: Variable Parameter zur Konfiguration des Leitungsmodells

| Leiterbreite                | W              | 0,254 mm |

|-----------------------------|----------------|----------|

| Leiterabstand               | S              | 0,254 mm |

| Höhe über Massefläche       | Ι              | 0,5 mm   |

| Leiterbahndicke             | Т              | 35 µm    |

| Konstante des Dielektrikums | ε <sub>r</sub> | 4,2      |

| Leiterlänge                 | Länge          | 50 mm    |

Tabelle 3: Platinenparameter

Die Berechnung der Gleich- und Gegentaktimpedanzen ist von zahlreichen physikalischen Eigenschaften der Streifenleitungen abhängig. Um die Vielzahl der Parameter einzugrenzen, werden zur Berechnung nur die in Abbildung 5 dargestellten Größen berücksichtigt. Die für eine typische Kfz-Elektronik exemplarisch gewählten physikalischen Eigenschaften können Tabelle 3 entnommen werden. Die Parametrisierung des Leitungsmodells wurde in dem in Abbildung 3 verwendeten Simulationsaufbau übernommen. Zusätzlich können 10 nF Kondensatoren als ESD-Schutzelemente an beiden Leitungen berücksichtigt werden. Der Aufbau ist in Abbildung 6 dargestellt.

| Abschluss                  | V <sub>Lade</sub><br>[kV] | V <sub>max</sub><br>[V] | I <sub>max</sub><br>[A] | Ε<br>[μJ] |

|----------------------------|---------------------------|-------------------------|-------------------------|-----------|

| Kein ESD-<br>Schutzelement | 8                         | 208,9                   | 27,8                    | 115,7     |

| 10 nF                      | 8                         | 66,0                    | 6,2                     | 52,1      |

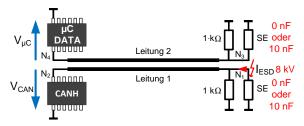

Abbildung 6: Simulationsaufbau Schutzelementen an beiden Leitungen

Tabelle 4: Simulierte Größen am CANH-Pin

Tabelle 4 enthält die simulierten Maximalspannungen und Ströme, sowie die Energien am CANH-Pin für eine 8 kV IEC-Generator-Entladung auf Leitung 1. Die am CANH-Pin simulierte Energie wird durch den Einsatz des 10 nF Kondensators um 50 % reduziert. Die in Leitung 2 eingekoppelten Signale am  $\mu$ C-Pin werden in Tabelle 5 miteinander verglichen. Nach Tabelle 1 beträgt die geringste Ausfallenergie für ein auf 1 kV HBM skaliertes IC-Modell etwa 350 nJ. Es werden für diese Konfiguration lediglich 3 nJ und 1 V Amplitude am  $\mu$ C-DATA-Pin für die 8 kV IEC-Generatorentladung simuliert. Der Sicherheitsfaktor ist somit größer als 100.

mit

| Abschluss              | V <sub>Lade</sub> [kV] | V <sub>max</sub> [V] | I <sub>max</sub> [A] | E [nJ] |

|------------------------|------------------------|----------------------|----------------------|--------|

| Kein ESD-Schutzelement | 8                      | 2,4                  | 0,1                  | 0,2    |

| 10 nF                  | 8                      | 1,1                  | 0,2                  | 3,3    |

Tabelle 5: Simulierte Größen am µC-DATA-Pin

### 1.8 Kritische Leitungstopologie

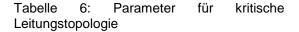

Nachfolgend werden kritische Konfigurationen untersucht, bei welchen lokale Pins mit einer spezifizierten HBM-Festigkeit von 1 kV oder 2 kV gefährdet sein können. Wie in Abschnitt 1.6 beschrieben wird, treten größere eingekoppelte ESD-Signale bei möglichst geringem Leiterabstand und großer Leitungslänge auf. Auch die Vergrößerung der Leiterbreite und des Abstandes zur Massefläche kann die Koppeleigenschaften zwischen den Leitern verbessern. Für die Simulation einer kritischen Konfiguration wurden die in Tabelle 6 gezeigten Parameter gewählt.

In dem in Abbildung 7 gezeigten Simulationsaufbau wird eine 8 kV IEC-ESD-Generator-Entladung auf Leitung 1 simuliert. Ein 10 nF Kondensator kann mit Knoten  $N_3$  an Leitung 2 verbunden werden. Tabelle 7 zeigt die Ergebnisse für die am  $\mu$ C-DATA-Pin an Leitung 2 simulierten Größen mit und ohne ESD-Schutzkondensator. Die Energie steigt um den Faktor 200 an, wenn ein ESD-Schutzelement mit Leitung 2 verbunden ist. Die Zerstörgrenze wird für diesen Fall bei auf 1 kV und 2 kV HBM

skalierten IC-Modellen überschritten. Ähnliche Energien werden simuliert, wenn die Positionen des µC und des Schutzelementes auf Leitung 2 vertauscht werden.

| Leiterbreite                | W              | 1 mm   |

|-----------------------------|----------------|--------|

| Leiterabstand               | S              | 0,1 mm |

| Höhe über Massefläche       | Н              | 1 mm   |

| Leiterbahndicke             | Т              | 35 µm  |

| Konstante des Dielektrikums | ε <sub>r</sub> | 4,2    |

| Leiterlänge                 | Länge          | 100 mm |

| V <sub>µC</sub> DATA                           | Leitung 2 | $1 \cdot k\Omega$ $N_3$ $N_3$ $N_3$ $N_3$ $N_3$ $N_3$ $N_3$ |

|------------------------------------------------|-----------|-------------------------------------------------------------|

| V <sub>CAN</sub> N <sub>2</sub> IIIIIIIII CANH | Leitung 1 | 1 kΩ IEC                                                    |

Abbildung 7: Kritische Konfiguration mit Schutzelement an Leitung 2

| Abschluss              | V <sub>Lade</sub> [kV] | V <sub>max</sub> [V] | I <sub>max</sub> [A] | E [nJ] |

|------------------------|------------------------|----------------------|----------------------|--------|

| Kein ESD-Schutzelement | 8                      | 4,0                  | 0,8                  | 5,8    |

| 10 nF                  | 8                      | 30,4                 | 14,8                 | 1202   |

Tabelle 7: Simulierte Größen am µC-DATA-Pin für kritische Leitungstopologie

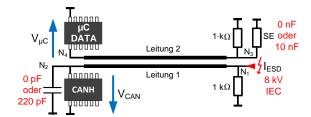

# 1.9 Kapazität an globalen Pins

Der Einfluss einer Kapazität an einem globalen IC-Pin auf die Einkopplung in eine benachbarte Leitung wird häufig diskutiert. In dem in Abbildung 8 gezeigten Simulationsaufbau kann eine 220 pF Kapazität parallel zum CANH-Pin geschaltet werden. Tabelle 8 enthält die am  $\mu$ C-Pin simulierten Parameter mit und ohne Kapazitäten an Knoten  $N_2$  und  $N_3$ . Die zusätzlich eingebrachte Kapazität am CANH-Pin verringert die ESD-Einkopplung in Leitung 2 nicht.

Abbildung 8: Kapazität an globalem CANH-Pin

| Abschluss                  | V <sub>Lade</sub><br>[kV] | V <sub>max</sub><br>[V] | I <sub>max</sub><br>[A] | E<br>[nJ] |

|----------------------------|---------------------------|-------------------------|-------------------------|-----------|

| Kein ESD-<br>Schutzelement | 8                         | 4,0                     | 0,8                     | 5,8       |

| 10 nF, 220 pF              | 8                         | 36.9                    | 15,8                    | 1246      |

Tabelle 8: Simulierte Größen am  $\mu$ C-DATA-Pin für Kapazitäten an Knoten  $N_2$  und  $N_3$

### 6 Zusammenfassung

Das Koppelverhalten von ESD-Ereignissen wurde untersucht. Für die Untersuchungen wurden IC-Pins charakterisiert und das elektrische Verhalten, sowie das thermische Ausfallverhalten bei ESD modelliert. Die Gefährdung von ICs durch Überkopplungen zwischen Leitungen wurde mit auf 1 kV und 2 kV HBM-Festigkeit skalierten Modellen untersucht. Die Leitungsverkopplung wurde für verschiedene Konfigurationen und Leitungstopologien mit und ohne diskrete ESD-Schutzelemente simuliert. Kritische Konfigurationen ergeben sich durch den Abschluss einer Leitung, in die ein ESD-Puls einkoppelt, mit niedriger Impedanz. Für diesen Fall konnten hohe Spannungs- und Stromamplituden simuliert und gemessen werden. Die skalierten IC-Modelle detektierten einen Ausfall. Eine deutliche Abschwächung des auf eine

benachbarte Leitung eingekoppelten Signals wird simuliert, wenn ein ESD-Schutzelement mit dem Knoten der Einspeisung des ESD-Pulses verbunden ist. Mit für Automobilelektronik typischen Leitungstopologien konnte kein IC-Ausfall durch Einkopplung einer 8 kV IEC-Generator-Entladung simuliert werden. Insgesamt ist die Gefahr durch Überkopplung durch eine Reduzierung der HBM-ESD-Festigkeit von lokalen IC-Pins als gering einzustufen. Jedoch können kritische Konfigurationen zu Problemen führen. Die ESD-Festigkeit von elektronischen Systemen sollte deshalb im Vorfeld durch eine Simulation abgesichert werden.

### Danksagung

Diese Arbeit wurde durch den ESD Forum e.V. unterstützt.

### Literatur

- [1] Industry Council on ESD Target Levels, "White Paper 1: A Case for Lowering Component Level HBM/MM ESD Specifications and Requirements", Oktober 2010

- [2] DKE Deutsche Kommission Elektrotechnik Elektronik Informationstechnik im DIN und VDE, AK 767.13.14\_2010-0015. Positionspapier ESD WP1, 2010

- [3] F. zur Nieden, Y. Cao, B. Arndt und S. Frei, "Vergleichbarkeit von ESD-Prüfungen auf IC- und Systemebene oder welchen Einfluss hat eine Reduzierung der IC-ESD-Festigkeit auf die Systemfestigkeit?", EMV 2010, Düsseldorf, März 2010

- [4] B. Arndt, F. zur Nieden, F. Müller, J. Edenhofer und S. Frei, "Virtual ESD Testing of Automotive Electronic Systems", APEMC 2010, Peking, China, April 2010

- [5] B. Arndt, F. Kremer, F. zur Nieden, Y. Cao und S. Frei, "Modellierung und Simulation von ESD-Schutzelementen mit VHDL-AMS", EMV 2010, Düsseldorf, März 2010

- [6] B. Arndt, F. zur Nieden, O. Iglitsyn und S. Frei, "Modellierung des thermischen Ausfallverhaltens von IC-Eingängen zur Bewertung der System-ESD-Festigkeit", ESD Forum, München, Dezember 2011

- [7] F. zur Nieden, B. Arndt, J. Edenhofer und S. Frei, "Vergleich von ESD-System-Level Testmethoden für Packaging und Handling", ESD-Forum 2009, Berlin, Dezember 2009

- [8] Y. Cao, B. Arndt, F. zur Nieden, F. Kremer, M. Stecher, und S. Frei, "Charakterisierung und systematische Bewertung von externen ESD Schutzelementen", EMV 2010, Düsseldorf, März 2010

- [9] K. Siebert, H. Günther, S. Frei und W. Mickisch, "Modeling of Frequency Dependent Losses of Transmission Lines with VHDL-AMS in Time Domain", International Zurich EMC Symposium, Schweiz, Januar 2009

- [10] O. Zinke und H. Brunswig: Hochfrequenztechnik 1, 6. Auflage, Berlin, Springer, 2000, ISBN 3-540-66405-X

- [11] Paul, Clayton R, "Analysis of Multiconductor Transmission Lines", New York, John Wiley & Sons Inc, 1994, ISBN 0-471-02080-X

- [12] http://web.awrcorp.com/, AWR Corporation, TX-Line™, 2011

- [13] High Power Pulse Instruments GmbH, <a href="http://www.hppi.de/products.html">http://www.hppi.de/products.html</a>, Oktober 2011

- [14] F. zur Nieden, S. Scheier und S. Frei, "Impact of Lowering the HBM-IC-Robustness on the Automotive-System-Level-Robustness", Bericht, September 2011